19.带奇偶校验的串行接收器

请参考:串行接收器及数据通路(2.2.5第18小结)

我们希望为串行接收器增加奇偶校验功能。奇偶校验会在每个数据字节之后添加一个额�外的位。我们将采用奇校验规则,即接收到的9位中1的个数必须为奇数。例如,序列101001011满足奇校验(其中有5个1),而001001011则不符合。

您需要调整现有的有限状态机(FSM)和数据通路,以执行奇偶校验。只有当字节被正确接收并且通过了奇偶校验时,才应设置“完成”信号(done)。与串行接收FSM一样,此FSM需要识别起始位,等待全部9位(数据位和奇偶校验位)接收完毕,然后验证停止位是否正确。如果在预期的时间点没有出现停止位,FSM必须等待直到检测到停止位后,再尝试接收下一个字节。

为您提供了一个用于计算输入流奇偶性的模块(它是一个带有复位的T触发器)。该模块的预期用途是接收输入的比特流,并在适当时间复位,以便对每个字节中的1的个数进行计数。

module parity (

input clk,

input reset,

input in,

output reg odd);

always @(posedge clk)

if (reset) odd <= 0;

else if (in) odd <= ~odd;

endmodule

请注意,串行协议中最低有效位(LSB)最先发送,奇偶校验位位于8个数据位之后。

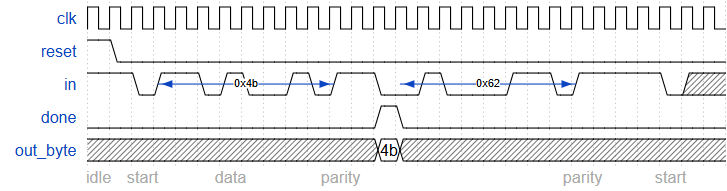

一些时序图的概念说明:

无帧错误情况下。第一字节奇偶校验通过,而第二字节奇偶校验失败。

模块声明

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output [7:0] out_byte,

output done

);